# Программные системы: теория и приложения

Двуязычный электронный научный журнал

№2  2024

*Bilingual Online Scientific Journal*

Program Systems:

Theory and Applications

Том 15 Выпуск 2(61) 2024 г.

## СОДЕРЖАНИЕ

*Научная статья* ПРОГРАММНОЕ И АППАРАТНОЕ ОБЕСПЕЧЕНИЕ РАСПРЕДЕЛЕННЫХ И СУПЕРКОМПЬЮТЕРНЫХ СИСТЕМ

Подлазов В. С.<sup>✉</sup>. Распределенная арифметика в оптическом канале на основе фотонных коммутаторов ..... 3–16, 17–19

*Научная статья* Искусственный интеллект и машинное обучение

АБРАМОВ Н. С., САТТАРОВА В. В., ФРАЛЕНКО В. П.<sup>✉</sup>, ХАЧУМОВ М. В.. Жестовое управление полетом малого беспилотного летательного аппарата ..... 21–33, 34–35

*Обзорная статья* Методы оптимизации и теория управления

ЯКУШЕВА С. Ф.<sup>✉</sup>, ХРИТАНКОВ А. С.. Систематический обзор методов составления тестовых инвариантов (Рус., Англ.) ..... 37–61, 62–86

*Научная статья* Искусственный интеллект и машинное обучение

СМЕТАНИН Ю. М.<sup>✉</sup>. Использование распределенных вычислений при моделировании предметной области в универсальной силлогистике ..... 87–110, 111–112

*Научная статья* Искусственный интеллект и машинное обучение

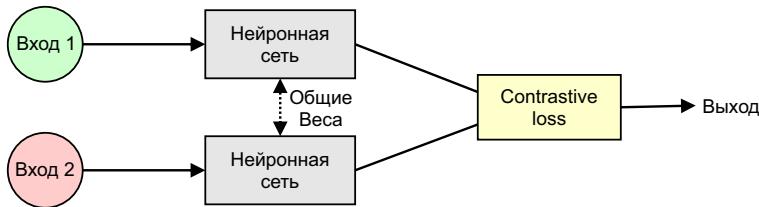

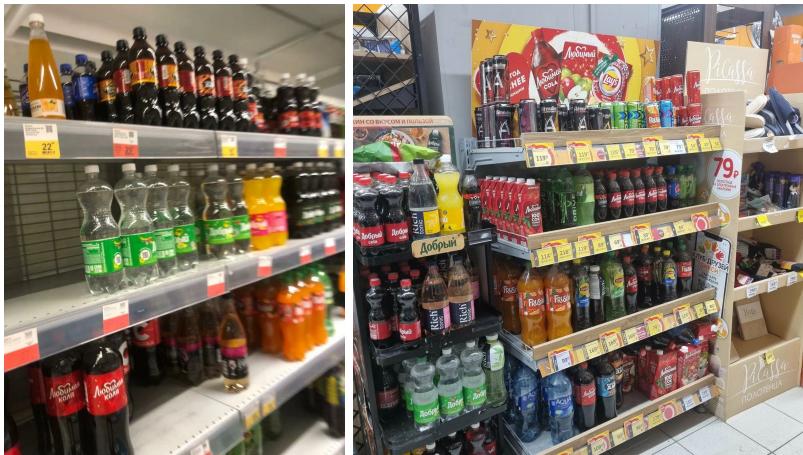

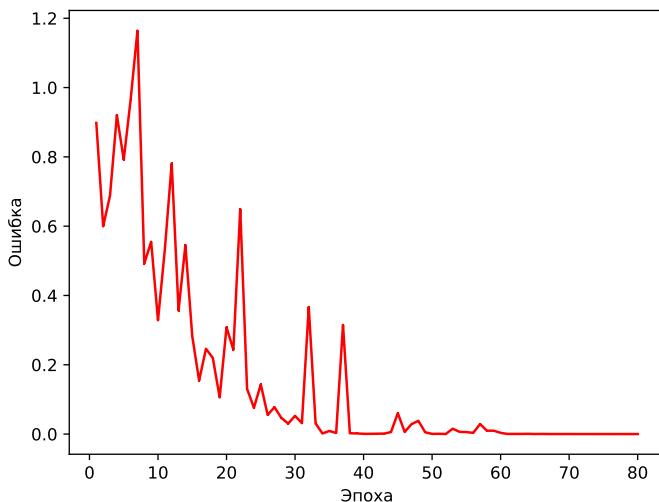

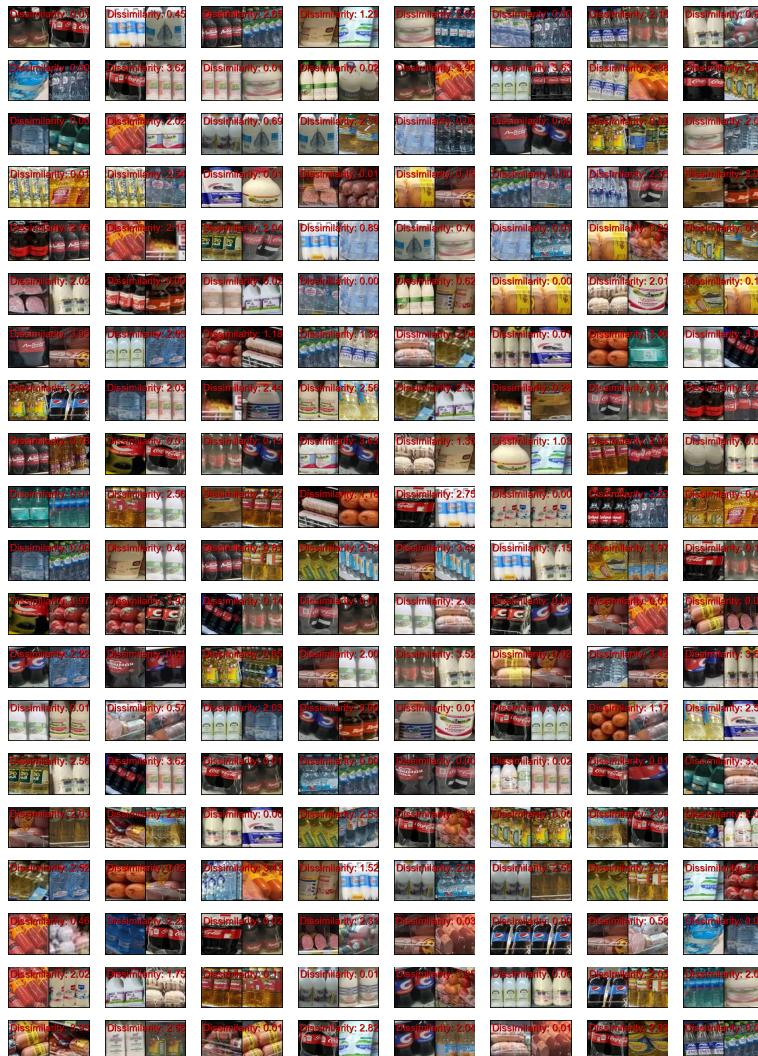

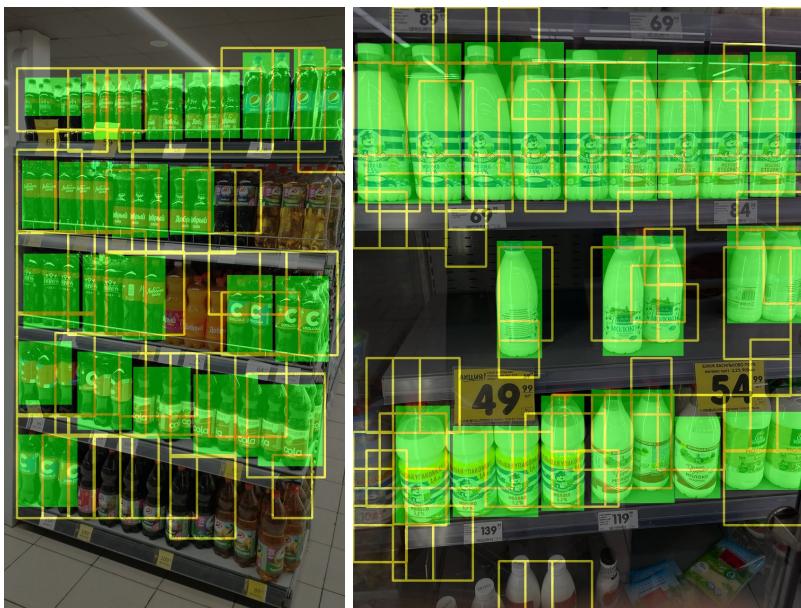

Смирнов А. В.<sup>✉</sup>, Тищенко И. П.. Применение нейронных сетей сиамской архитектуры в задачах классификации продуктов различных категорий на прилавках универмага ..... 113–135, 136–137

*Обзорная статья* ПРОГРАММНОЕ И АППАРАТНОЕ ОБЕСПЕЧЕНИЕ РАСПРЕДЕЛЕННЫХ И СУПЕРКОМПЬЮТЕРНЫХ СИСТЕМ

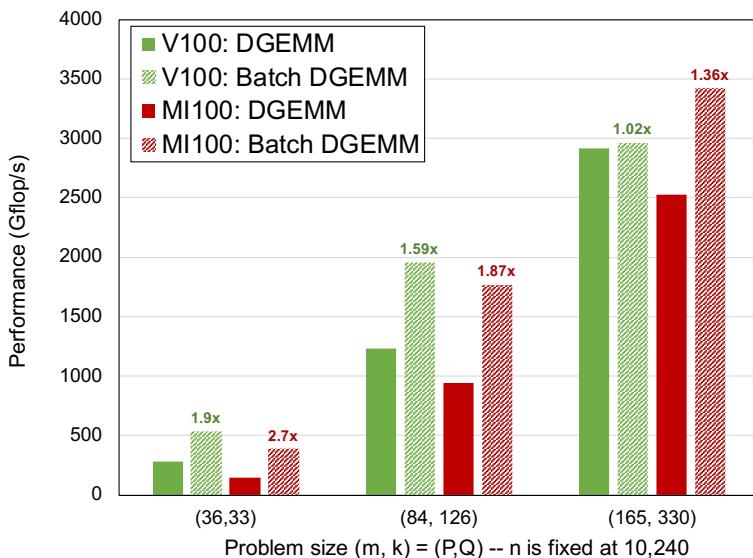

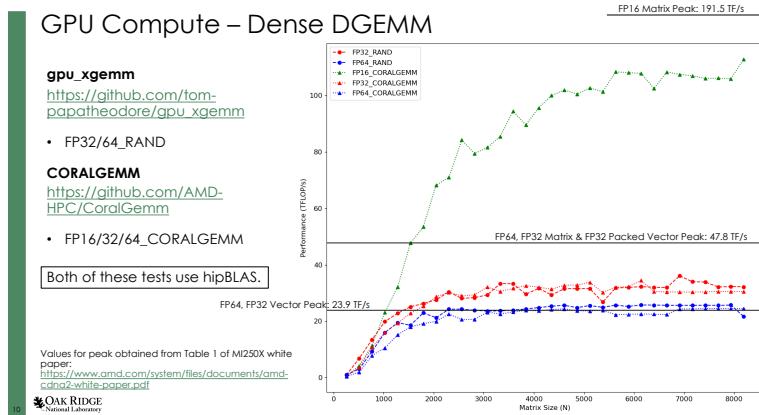

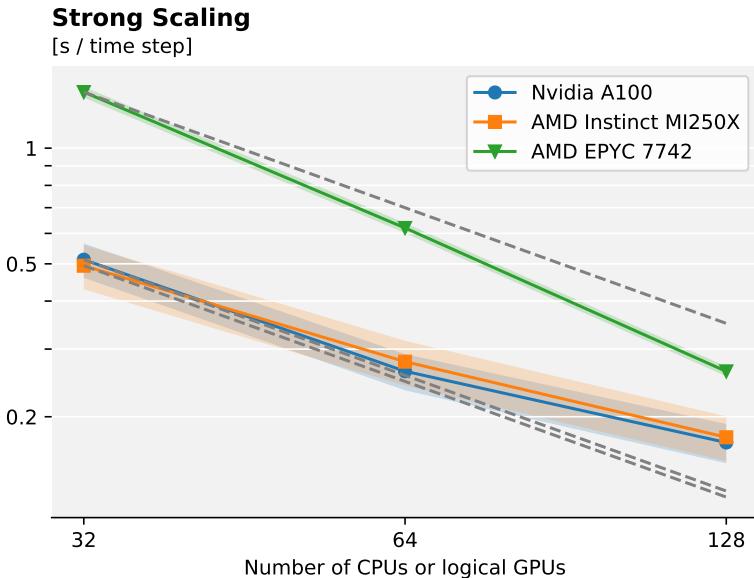

Кузьминский М. Б.<sup>✉</sup>. Новое поколение GPGPU и сопутствующего оборудования: микроархитектура и производительность вычислительных систем от серверов до суперкомпьютеров (Рус., Англ.) ..... 139–305, 306–473

*Научная статья* Медицинская информатика

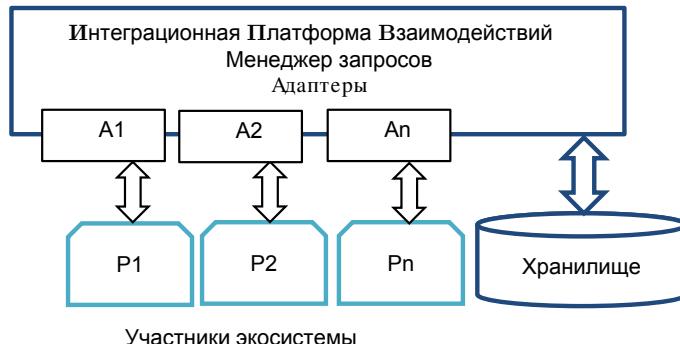

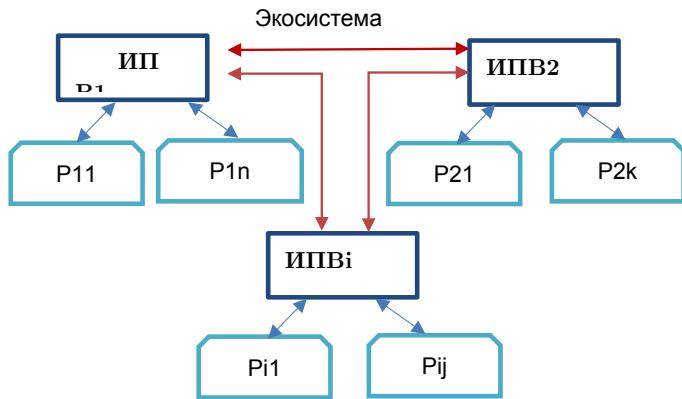

Малых В. Л.<sup>✉</sup>, Калинин А. Н., Рудецкий С. В.. Архитектура взаимодействия в медицинской экосистеме ..... 475–490, 491–492

*Авторский указатель* ..... 493

Click the flag at a top corner of any page to switch the language, please!

*Author index* ..... 495

*Contents* ..... 496

## Распределенная арифметика в оптическом канале на основе фотонных коммутаторов

Виктор Сергеевич **Подлазов**<sup>✉</sup>

Институт проблем управления имени В. А. Трапезникова РАН, Москва, Россия

**Аннотация.** В статье рассматривается фотонная сеть с распределенным управлением, состоящая из нескольких узлов, связанных общим каналом, в котором за время передачи одного числа выполняется единая операция над числами, которые параллельно передаются всеми узлами. Рассматриваются такие операции как суммирование или нахождение максимума (минимума) чисел, передаваемых последовательно по двоичным разрядам. Предполагается, что разряды чисел передаются парафазными оптическими сигналами, а общий канал строится из фотонных коммутаторов этих сигналов.

**Ключевые слова и фразы:** общий канал, распределенное управление, фотонный коммутатор, фотонные мультиплексор и демультиплексор, вычисление в общем канале, последовательные числа

**Для цитирования:** Подлазов В. С. *Распределенная арифметика в оптическом канале на основе фотонных коммутаторов* // Программные системы: теория и приложения. 2024. Т. 15. № 2(61). С. 3–19. [https://psta.psiras.ru/read/psta2024\\_2\\_3-19.pdf](https://psta.psiras.ru/read/psta2024_2_3-19.pdf)

## Введение

Развитие компьютерной элементной базы привело к появлению проектов фотонных компьютеров и фотонных элементов для них [1, 2]. Продолжением этой тенденции стало развитие проектов систем на основе локальных сетей, в которых данные передаются вместе с командами, образуя spatial data flow структуры [3]. Их частным случаем являются структуры с распределенной параллельной обработкой данных во время и в процессе их передачи – вычисления в общем канале (ВОК) [4].

При ВОК выполняется групповая операция над множеством чисел, передаваемых узлами параллельно, за время передачи по общему каналу сети одного числа (результата операции). При этом эта операция выполняется без промежуточных буферизаций промежуточных значений результата. Последнее свойство обеспечивает превосходство ВОК по быстродействию над традиционным сетевыми реализациями распределенных вычислений, которые требуют последовательных передач нескольких чисел и последовательного выполнения нескольких операций над ними.

Операция ВОК выполняется на аппаратном уровне за время пересылки по каналу сети только одного числа – формирующегося результата операции. Эта операция выполняется без тактовых задержек в функциональных блоках при узлах сети, состоящих из нескольких фотонных коммутаторов выбранного вида.

Традиционное выполнение распределенных операций складывается из нескольких последовательных передач чисел между узлами сети и арифметических операций над ними. Конкретно: распределенная операция над  $N$  числами может быть выполнена одним из двух крайних способов. Во-первых, это последовательная пересылка ( $N - 1$ ) числа с промежуточными ( $N - 1$ ) операцией над ними. Во-вторых, это парные передачи чисел, выполняемые параллельно за  $\log_2 N$  последовательных их передач и за такое же количество операций в узлах. При этом указанные действия выполняются программным образом, что многократно увеличивает время их исполнения.

Ниже рассматривается реализация операций ВОК в оптическом канале с фотонными коммутаторами для использования таких широко известных его преимуществ как малое энергопотребление, высокая помехозащищенность и более высокие частоты передачи, связанные с независимостью параметров оптических сигналов от свойств окружающей среды.

Далее рассматриваются реализации операций ВОК на вынесенных из узлов функциональных блоках, составленных из выбранных фотонных

коммутаторов, и способ выполнения операций в них, который не использует обратной связи с узлами в процессе выполнения операций.

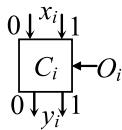

Для выполнения операций ВОК значение каждой логической переменной передается по каналу в парофазном виде, т.е. по двум линиям 0 и 1. Значение 0 передается сигналом в линии 0 при отсутствии сигнала в линии 1, а значение 1 – сигналом в линии 1 при отсутствии сигнала в линии 0. Линии 0 и 1 проходят через конвертер  $C_i$  каждого  $i$ -го узла сети (рисунок 1). Каждый конвертер выполняет унарную операцию  $O_i$  преобразования входной переменной  $x_i$  в выходную логическую переменную  $y_i = O_i x_i$ .

Рисунок 1. Конвертор фотонных переменных

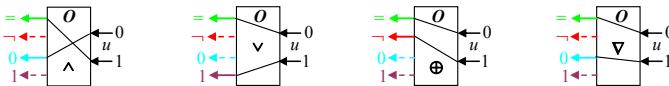

Операция  $O_i$  выполняет следующие преобразования: повторения  $y_i = x_i$  ( $\ll=$ ), отрицания  $y_i = \neg x_i$  ( $\ll\neg$ ), перевода в значение  $y_i = 0$  ( $\ll 0$ ) и перевода в значение  $y_i = 1$  ( $\ll 1$ ). Состояния конвертера  $C_i$  при выполнении операции  $O_i$  представлены на рисунке 2.

$$O_i: \{\ll=, \ll\neg, \ll 1, \ll 0\}$$

Рисунок 2. Состояния операции  $O_i$  конвертера  $C_i$

Операция  $O_i$  в свою очередь задается по значению управляющей логической переменной  $u_i$ , выдаваемой  $i$ -м узлом сети. В результате конвертер  $C_i$  выполняет бинарную операцию  $y_i = x_i \cdot u_i$ , которая может быть любой из 16 бинарных логических операций. В таблицах 1а– 2б приводятся таблицы истинности ряда используемых логических операций.

ТАБЛИЦА 1. Таблицы истинности операций  $\vee$  и  $\wedge$

(а) функция «И» ( $\wedge = \wedge$ )

| $x$ | $u$ | $O$     | $y$ |

|-----|-----|---------|-----|

| 0   | 0   | $\ll 0$ | 0   |

| 0   | 1   | $\ll=$  | 0   |

| 1   | 0   | $\ll 0$ | 0   |

| 1   | 1   | $\ll=$  | 1   |

(б) функция «ИЛИ» ( $\wedge = \vee$ )

| $x$ | $u$ | $O$     | $y$ |

|-----|-----|---------|-----|

| 0   | 0   | $\ll=$  | 0   |

| 0   | 1   | $\ll 1$ | 1   |

| 1   | 0   | $\ll=$  | 1   |

| 1   | 1   | $\ll 1$ | 1   |

Таблица 2. Таблицы истинности операций  $\oplus$  и  $\nabla$ (a) функция «Сложение по mod2» ( $\aleph = \oplus$ )

| $x$ | $u$ | $O$         | $y$ |

|-----|-----|-------------|-----|

| 0   | 0   | $\ll=$      | 0   |

| 0   | 1   | $\ll\!\neg$ | 1   |

| 1   | 0   | $\ll=$      | 1   |

| 1   | 1   | $\ll\!\neg$ | 0   |

(b) функция «Начальный запуск» ( $\aleph = \nabla$ )

| $x$ | $u$ | $O$     | $y$ |

|-----|-----|---------|-----|

| 0   | 0   | $\ll=$  | 0   |

| 0   | 1   | $\ll 0$ | 0   |

| 1   | 0   | $\ll=$  | 1   |

| 1   | 1   | $\ll 0$ | 0   |

При линейном размещение  $N$  узлов сети и последовательном размещении их конвертеров можно за время передачи по общему каналу одного числа образовать в нем сумму размещенных по узлам чисел или выделить из них максимальное число [4]. Для этого числа передаются как двоичные числа последовательно по разрядам. Для суммирования они передаются младшими разрядами вперед и используются операции  $\oplus$  и  $\wedge$  для образования двоичной суммы и значения переноса в следующий разряд соответственно. Для нахождения максимального числа все числа передаются старшими разрядами вперед, и в ней используется операция  $\vee$ .

Представленная схема позволяет выполнять арифметические и логические операции над значениями, представленными фотонными сигналами, на базе коммутаторов без использования специальных фотонных арифметико-логических устройств типа [1]. Саму сеть можно образовать из двух ветвей (восходящей и нисходящей) с подключением каждого узла к обеим ветвям. Восходящая ветвь используется для образования результата, а нисходящая ветвь – для оповещения всех о нем. Можно также использовать кольцевую сегментированную сеть с двукратной передачей чисел – для образования результата и оповещения о нем.

Сеть для ВОК можно построить из оптоэлектронных переключателей на базе интерферометров Маха-Зандера [5]. Их более практическая форма представлена в [6]. Из таких переключателей можно собрать оптоэлектронный коммутатор  $4 \times 4$ , в котором передача данных через коммутатор ведется оптическими сигналами, а управление коммутатором осуществляется узлом сети электронным образом [7]. В настоящее время быстродействие таких переключателей доходит до 100 Гбит/сек [8] и они имеют достаточно высокую плотность упаковки [9].

Однако построение ВОК на оптоэлектронных переключателях имеет своим недостатком необходимость преобразования значений разрядов между оптической и электронной формами в процессе выработки управляющих воздействий в каждом разряде на основе результата из предыдущего разряда. Этот недостаток, во-первых: снижает быстродействие фотонных коммутаторов до быстродействия электронных коммутаторов и, во-вторых, увеличивает их энергопотребление.

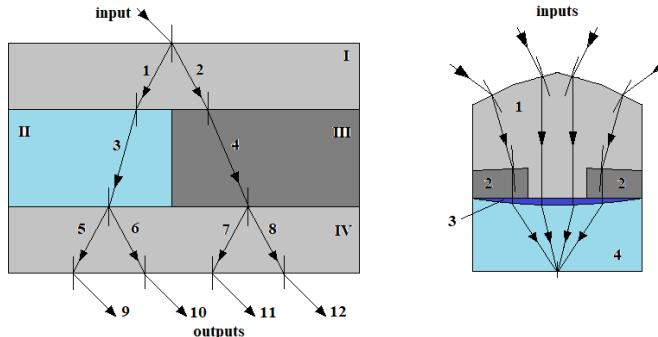

В статье рассматривается возможность выполнения операций ВОК на базе разных фотонных элементов без использования внешних оптоэлектронных преобразований. В качестве базовых фотонных элементов можно использовать фотонные демультиплексор  $D 1 \times 4$  и мультиплексор  $M 4 \times 1$ , собираемые из нескольких слоев тонких пленок с электрооптическими или магнитооптическими свойствами (рисунок 3) [10, 11].

Рисунок 3. Структура коммутационных ячеек (демультиплексор и мультиплексор), основанных на оптически прозрачных метаматериальных и ферритовых пленках

Особенность их применения состоит в том, что для управления коммутацией используется два оптических сигнала на разных частотах  $\lambda_1$  и  $\lambda_2$ . В демультиплексоре они преобразуются в 4 управляющих сигнала электронной или магнитной природы и подаются на два направляющих слоя, каждый из которых задает два направления распространения информационного сигнала, поступившего на его оптический вход. В результате входной оптический сигнал направляется на один из 4-х оптических выходов.

Заметим, что эти элементы в совокупности с одноразрядными фотонными линиями задержки были использованы для построения фотонных неблокируемых системных сетей [12, 13].

## 1. Набор необходимых фотонных элементов

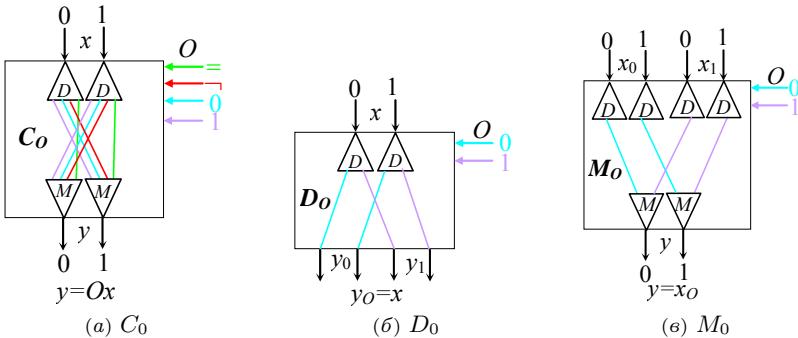

Управляемый фотонный конвертер  $C_0$  собирается из двух демультиплексоров  $D$  и двух мультиплексоров  $M$  (рисунок 4 $a$ ). В каждом демультиплексоре используется 4 управляющих сигнала, определяющих для конвертера значение управляющей операции  $O$  и задающих выходы демультиплексора. Например, значения «0» и «1» подаются на первый направляющий слой, а значения «=» и «¬» – на второй слой.

В дальнейшем наряду с конвертером  $C_0$  используются управляемые демультиплексор  $D_0$  (рисунок 4 $b$ ) и мультиплексор  $M_0$  (рисунок 4 $c$ ), построенные аналогичным образом.

Рисунок 4. Схемы управляемых фотонного конвертера  $C_0$ , демультиплексора  $D_0$  и мультиплексора  $M_0$

Образование значений операции  $O$  из значений управляющей фотонной переменной и задается схемами на рисунке 5. Эти схемы можно заменить

Рисунок 5. Схема образования значений операции О

на одну универсальную с использованием коммутатора с электронным управлением [7] от узла сети. Однако для простоты в данной работе используются разные неуправляемые схемы реализации операции  $O$ .

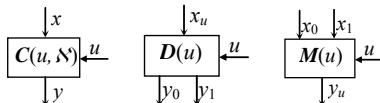

Как результат соединения схем рисунка 4а и схемы рисунка 5 управляемый конвертер будет обозначаться как 2-входовая схема с передаваемой переменной  $x$ , управляющей переменной  $u$  и реализуемой логической функцией  $C(u, \aleph)$  (рисунок 6). При этом переменная  $x$  обозначается стрел-

Рисунок 6. Окончательное обозначение управляемых конвертера  $C(u, \aleph)$ , демультиплексора  $D(u)$  и мультиплексора  $M(u)$

кой «ласточкин хвост», а переменная  $u$  – прямой стрелкой. Аналогично, управляемые демультиплексор и мультиплексор, полученные объединением схем рисунка 4, будут обозначаться как  $D(u)$  и  $M(u)$  (рисунок 6).

## 2. Распределенный фотонный сумматор

Для выполнения фотонной операции ВОК «сумма» при каждом узле сети формируется свой исполнительный блок  $U$ , состоящий из ранее определенных конвертеров и мультиплексоров, который осуществляет преобразования значений разрядов передаваемых чисел.

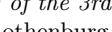

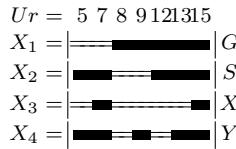

Первый узел сети выдает по парафазной линии значений в свой блок  $U_2$  слот  $X_1$ , содержащий двоичное многоразрядное число, начиная с младших разрядов, а по парафазной синхролинии – слот  $S$  той же разрядности. Передача слота  $S$  начинается с передачи его метки  $s^0$ , которая задается одновременной передачей значений 0 и 1, т.е. передачей сигналов по обеим парафазным линиям. Прохождение метки  $s^0$  запускает передачу слотов  $X_1$  и  $S$ , которые передаются синхронно по разрядам. В слоте  $X_1$  разряды передаются переменными  $x_1^i$ , а в слоте  $S$  – переменными  $s^i$ , где  $i$  – это номер разряда. Первый разряд слота  $S$  имеет значение 1 ( $s^1 = 1$ ), а остальные его разряды – значения 0 ( $s^i = 0$  при  $i > 1$ ).

Любой другой узел сети ( $1 < k \leq N$ ) передает по линии значений в свой блок  $U_k$  слот  $X_k$ , содержащий значения переменных  $x_k^i$  для каждого разряда. Кроме того, в этот блок поступает слот  $S$ , прошедший через исполнительный блок предыдущего узла. Прохождение метки  $s^0$  запускает в узле  $k$  передачу слота  $X_k$ , что поразрядно синхронизирует его в блоке  $U_k$  со слотом  $S$ .

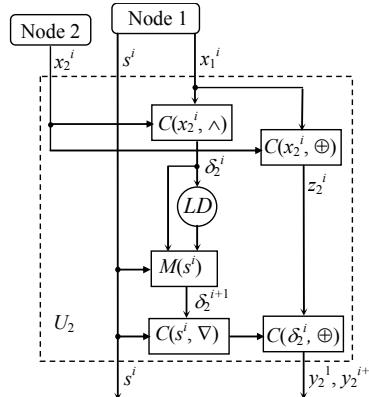

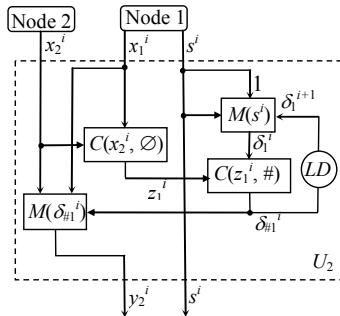

На рисунке 7 представлена схема блока  $U_2$ , подсоединяемого к первому и второму сетевым узлам распределенного сумматора. Точки на линиях

Рисунок 7. 2-узловой распределенный сумматор

обозначают узлы разделения световых сигналов посредством ветвления оптических линий. Проблема ослабления оптических сигналов может быть решена посредством использования фотонных усилителей на выходе блоков  $U_k$  [14].

На его входы  $U_2$  подаются слот  $S$  и слоты  $X_1$  и  $X_2$ , а на выходе образуется слот  $Y_2$ , содержащий сумму чисел из слотов  $X_1$  и  $X_2$ . В этом блоке на конвертере  $C(x_2^i, \oplus)$  складываются по mod2 значения переменных  $x_1^i$  и  $x_2^i$ , образуя промежуточный результат в виде переменной  $z_2^i$ . На конвертере  $C(x_2^i, \nabla)$  из переменных  $x_1^i$  и  $x_2^i$  образуется переменная  $\delta_2^i$ , которая после прохождения по линии задержки  $LD$  длительностью

в один разряд, образует переменную  $\delta_2^{i+1}$ , задающую значение переноса в следующий разряд. Через мультиплексор  $M(s^i)$  пропускается значение  $\delta_2^1$  в первом разряде и  $\delta_2^{i+1}$  в любом другом разряде. Через конвертер  $C(s^i, \nabla)$  проходят переменные  $\delta_2^1$  и  $\delta_2^{i+1}$ . Конвертор обнуляет первую из них и пропускает вторую без изменения (таблица 2б) для остальных разрядов. Конвертор  $C(\delta_2^i, \oplus)$  образует окончательный результат поразрядных вычислений в виде переменных  $y_2^i$ , составляющих слот  $Y_2$ .

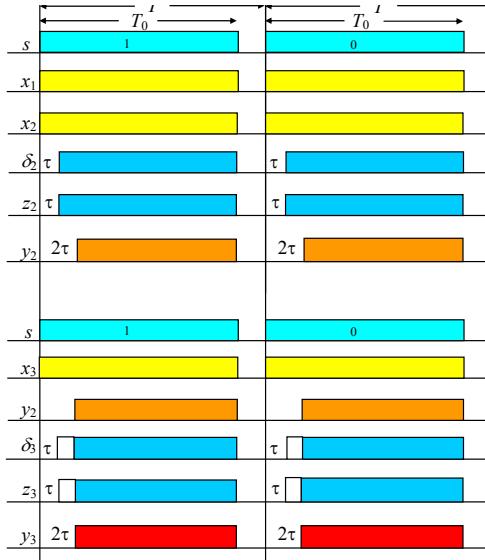

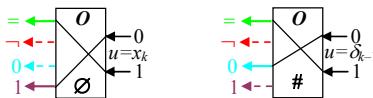

На рисунке 8 (верхняя половина) представлена временная диаграмма

Рисунок 8. Временная диаграмма распределенного сумматора работы блока  $U_2$  в первых двух разрядах с использованием следующих обозначений.

Период разряда задается как  $T$ , длительность активных сигналов в нем – как  $T_0$ , а время настройки конвертера или мультиплексора по управляющей переменной  $u$  – как  $\tau$ . Необходимо отметить, что переменная  $\delta_2^i$  проходит устройства  $M(s^i)$  и  $C(s^i, \nabla)$  без задержки, так как они уже настроились к моменту ее появления. Как результат выходная переменная  $y_2^i$  во всех разрядах появляется с задержкой на  $2\tau$  и задается сигналами длительности  $T_0 - 2\tau$ .

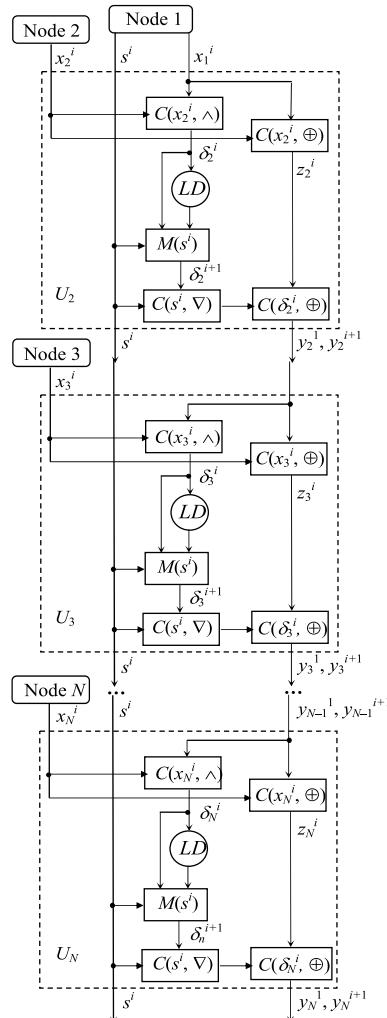

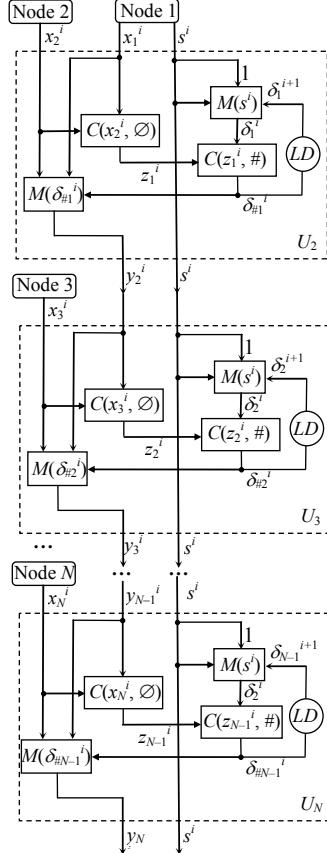

На рисунке 9 представлена схема  $N$ -узлового распределенного фотонного сумматора. На входы блока  $U_k$  ( $k > 2$ ) подаются слот  $S$  и слоты  $Y_{k-1}$  и  $X_k$ , а на выходе образуется слот  $Y_k$ . Работа всех блоков синхронизируется слотом  $S$ , и все операции в блоках выполняются параллельно относительно 1-го разряда слота  $S$ .

Рисунок 9.  $N$ -узловой распределенный сумматор

На рисунке 8 представлена также (нижняя половина) временная диаграмма работы блоков  $U_2$  и  $U_3$  сумматора в первых двух разрядах и в тех же обозначениях. Следует отметить, что нижняя половина диаграммы справедлива для любого блока  $U_k$  при  $k > 2$ . Это означает, что выходная переменная  $y_k^i$  появляется с задержкой на  $2\tau$  относительно начала синхросигналов  $s_i$  при любых  $k$  и  $i$ , т.е. при любом числе узлов и во всех разрядах чисел и задается сигналами длительности  $T_0 - 2\tau$ .

### 3. Распределенный фотонный «максимизатор»

Для выполнения фотонной операции ВОК «максимум» при каждом узле сети формируется свой исполнительный блок  $U$ , который осуществляет преобразования значений разрядов передаваемых чисел.

Первый узел сети по парафазной линии значений выдает в свой блок  $U$  слот  $X_1$ , содержащий двоичное многоразрядное число, начиная со старших разрядов, а по парафазной синхролинии – слот  $S$  той же разрядности. Любой другой узел  $k$  сети ( $1 < k \leq N$ ) передает по линии значений в свой блок  $U_k$  слот  $X_k$ , содержащий переменные  $x_k^i$ , начиная со старшего разряда. Кроме того, в этот блок поступает слот  $S$ , прошедший через исполнительный блок предыдущего узла.

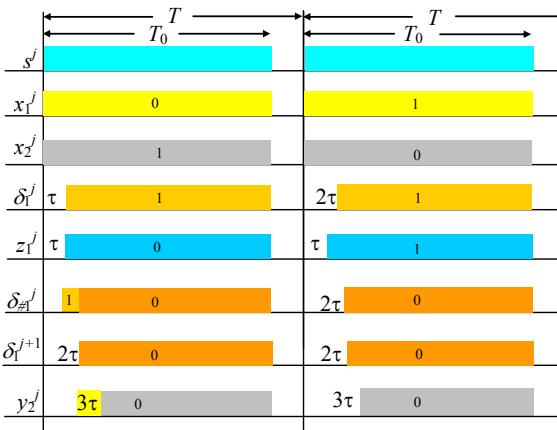

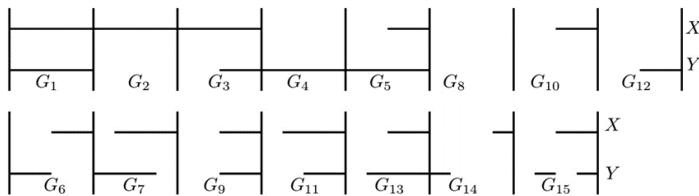

На рисунке 10 представлена схема блока  $U_2$ , подсоединяемого к первому и второму сетевым узлам распределенного «максимизатора». На его входы подаются слот  $S$  и слоты  $X_1$  и  $X_2$ , а на выходе образуется слот  $Y_2$ , содержащий максимальное число из слотов  $X_1$  и  $X_2$ .

Рисунок 10. 2-узловой распределенный «максимизатор»

По значениям синхросигнала  $s^i$  посредством мультиплексора  $M(s^i)$  формируется начальное значение переменной  $\delta_1^1 = 1$ , которая играет роль переменной состояния «максимизатора» во всех разрядах  $i \geq 1$ . Переменная  $\delta_1^i$  должна находиться в значении  $\delta_1^i = 1$  для всех разрядов  $i < j$ , для которых  $x_1^i \geq x_2^i$ , и находиться в значении  $\delta_1^i = 0$  для всех разрядов  $i > j$  после разряда  $j$ , для которого  $x_1^j < x_2^j$ . Такую последовательность значений  $\delta_1$  формируют конвертеры  $C(x_2^i, \emptyset)$  и  $C(z_1^i, \#)$  совместно с мультиплексором  $M(s^i)$  и линией задержки LD на один разряд. Первый конвертер по значениям переменных  $x_1^i$  и  $x_2^i$  формирует значение промежуточной переменной  $z_1^i$ , реализуя логическую функцию «Переключение» по таблице За при  $k \geq 2$ . Второй конвертер формирует значение переменной  $\delta_{\#1}^i$ , реализуя логическую функцию «Повторение» по таблице 3б при  $k \geq 2$ .

Мультиплексор  $M(s^i)$  и линия задержки LD образуют значения переменной  $\delta_1^{i+1} = \delta_{\#1}^i$  для следующего разряда. При этом схема об-

ТАБЛИЦА 3. Таблицы истинности для блока  $U_k$  ( $k \geq 2$ )(a) функция «Переключение»

( $\aleph = \emptyset$ )(b) функция «Повторение»

( $\aleph = \#$ )

| $x_{k-1}$ | $x_k$ | $O$ | $z_{k-1}$ |

|-----------|-------|-----|-----------|

| 0         | 0     | «0» | 1         |

| 0         | 1     | «=» | 0         |

| 1         | 0     | «0» | 1         |

| 1         | 1     | «=» | 1         |

| $z_{k-1}$ | $\delta_{k-1}$ | $O$ | $\delta_{\#(k-1)}$ |

|-----------|----------------|-----|--------------------|

| 0         | 0              | «=» | 0                  |

| 0         | 1              | «1» | 0                  |

| 1         | 0              | «=» | 0                  |

| 1         | 1              | «1» | 1                  |

разования значений операции  $O$  (см. Введение) задается рисунком 11 (аналогом рисунка 5). Для тех разрядов  $i < j$ , для которых сохраняется

Рисунок 11. Схема образования значений операции  $O$

значение  $\delta 1 = 1$ , через мультиплексор  $M(\delta_{\#1}^i)$  формируется значение выходной переменной  $y_2^i = x_1^i$ . Однако, для тех разрядов  $i > j$ , для которых сохраняется значение  $\delta 1 = 0$ , через мультиплексор  $M(\delta_{\#1}^i)$  формируется значение выходной переменной  $y_2^i = x_2^i$ . При этом для разряда  $j$  формируется значение  $y_2^j = x_2^j = 1$ .

На рисунке 12 приводится временная диаграмма формирования разных переменных для разрядов  $j$  и  $j + 1$ , где  $\tau$  обозначает время настройки конвертеров и мультиплексора, а  $T$  и  $T_0$  – длительности разряда и активного сигнала в нем. Видно, что активный сигнал укорачивается на время не большее  $3\tau$ , которое не зависит от значения  $j$ .

Рисунок 12. Временная диаграмма 2-узлового «максимизатора» для  $j$ -го разряда

На рисунке 13 приводится схема  $N$ -узлового распределенного «максимизатора». Каждый блок  $U_k$  ( $k > 2$ ) повторяет блок  $U_2$  с заменой

Рисунок 13.  $N$ -узловой распределенный «максимизатор»

$x_1$  на  $y_{k-1}$  и заменой индекса 2 на индекс  $k$ . При этом длительность активного сигнала  $T_0 - 3\tau$  не зависит от значения  $k$ .

### Заключение

В статье показана принципиальная реализуемость распределенных операций ВОК «максимум» и «сумма» на основе фотонных коммутаторов с парафазным представлением значений логических переменных. Также на основе этих операций можно осуществлять в сети [4] сортировку массива чисел за время передачи  $N$  чисел; умножение чисел за время передачи одного числа; скалярное произведение  $N$  чисел за время передачи двух чисел и ряд других операций. Все они являются операциями

магистрального (трубопроводного) типа.

В неблокируемых сетях с прямыми каналами [15, 16] можно организовывать множество таких операций, дополнительно размещая в слотах данных адреса узлов и коды операций, реализуемые в них. Способы построения таких сетей и способы реализации в них множества магистральных операций это тема отдельной работы.

## Список использованных источников

- [1] Stepanenko S. *Structure and Implementation Principles of a Photonic Computer* // EPJ Web of Conferences.– 2019.– Vol. 224.– id. 04002.– 7 pp. doi [↑4, 6](#)

- [2] Степаненко С. А. *Оптический логический элемент (варианты)*, Патент № 2 723 906 С1.– 18.06.2020.– ид. 06. [↑4](#)

- [3] Абрамов С. М., Степаненко С. А. *О подходах к разработке программного обеспечения для фотонной вычислительной машины*, Национальный Суперкомпьютерный Форум (НСКФ-2023) (Россия, Переславль-Залесский, ИПС имени А.К. Айламазяна РАН, 28 ноября–01 декабря 2023 года). url [↑4](#)

- [4] Прангишвили И. В., Подлазов В. С., Стецюра Г. Г. *Локальные микропроцессорные вычислительные сети*, Глава 6.– М.: Наука.– 1984.– 175 с. [↑4, 6, 14](#)

- [5] Stanley A. I., Singh G., Eke J., Tsuda H. *Mach-Zehnder interferometer: A review of a perfect all optical switching structure* // Proceedings of the International Conference on Recent Cognizance in Wireless Communication & Image Processing, eds. Afzalpulkar N., Srivastava V., Singh G., Bhatnagar D., New Delhi: Springer.– 2016.– ISBN 978-81-322-2638-3.– Pp. 415–425. doi [↑6](#)

- [6] Sacher W. D., Green W. M. J., Gill D. M., Assefa S., Barwicz T., Khater M., Kiewra Ed., Reinholm C., Shank S. M., Vlasov Yu. A., Poon J. K. S. *Binary phase-shift keying by coupling modulation of microrings* // Optics Express.– 2014.– Vol. 22.– No. 17.– Pp. 20252–20259. doi [↑6](#)

- [7] Green W. M. J., Yang M., Assefa S., Van Campenhout J., Lee B. G., Jahnes C. V., Doany F. E., Schow C. L., Kash J. A., Vlasov Y. A. *Silicon electro-optic 4 × 4 non-blocking switch array for on-chip photonic networks* // Los Angeles, California United States, 6–10 March 2011, OSA/OFC/NFOEC 2011.– ISBN 978-1-55752-906-0.– id. OThM1. doi [↑6, 8](#)

- [8] Yen T.-H., Hung Y.-J. *Fabrication-insensitive CWDM (de)multiplexer based on cascaded Mach-Zehnder interferometers on silicon-on-insulator* // Journal of Lightwave Technology.– 2020.– Vol. 39.– No. 1.– Pp. 146–153. doi [↑6](#)

- [9] Gui Y., Nouri B. M., Miscuglio M., Amin R., Wang H., Khurjin J. B., Dalir H., Sorger V. J. *100 GHz micrometer-compact broadband monolithic ITO Mach-Zehnder interferometer modulator enabling 3500 times higher packing density* // Nanophotonics.– 2022.– Vol. 11.– No. 17.– Pp. 4001–4009. doi [↑6](#)

- [10] Vytovtov K., Barabanova E., Zouhdhi S. *Optical switching cell based on metamaterials and ferrite films*, 12th International Congress on Artificial Materials for Novel Wave Phenomena (Metamaterials) (Espoo, Finland, August 2018–01 September 2018).– 2018.– Pp. 424–426. doi [↑7](#)

- [11] Barabanova E. A., Vytovtov K. A. *The control system elements of the new generation optical switching cell* // Journal of Physics: Conference Series.– 2019.– Vol. **1368**.– No. 2.– id. 022002.– 9 pp. doi ↑<sub>7</sub>

- [12] Vytovtov K. A., Barabanova E. A., Podlazov V. S. *Model of next-generation optical switching system* // Distributed Computer and Communication Networks, DCCN 2018, Communications in Computer and Information Science.– vol. **919**, Cham: Springer.– ISBN 978-3-319-99447-5.– Pp. 377–386. doi ↑<sub>7</sub>

- [13] Barabanova E. A., Vytovtov K. A., Vishnevskiy V. M., Podlazov V. S. *High-capacity strictly non-blocking optical switches based on new dual principle*, 5th International Scientific Conference on Information, Control, and Communication Technologies (ICCT-2021) (Astrakhan, Russian Federation, 4–7 October 2021) // Journal of Physics: Conference Series.– 2021.– Vol. **2091**.– id. 012040.– 17 pp. doi ↑<sub>7</sub>

- [14] Roelkens G., Raz O., Green W. M. J., Assefa S., Tassaert M., Keyvaninia S., Vandoorne K., Van Thourhout D., Baets R., Vlasov Y. *Towards a low-power nanophotonic semiconductor amplifier heterogeneously integrated with SOI waveguides*, 7th IEEE International Conference on Group IV Photonics (Beijing, China, 01–03 September 2010).– Pp. 16–18. doi ↑<sub>9</sub>

- [15] Подлазов В. С. *Самомаршрутизируемая неблокируемая системная сеть с прямыми каналами: сложность и быстродействие* // Программные системы: теория и приложения.– 2022.– Т. **13**.– № 4(55).– С. 47–76. doi URL ↑<sub>15</sub>

- [16] Подлазов В. С. *Разные неблокируемые самомаршрутизируемые системные сети с прямыми каналами* // Программные системы: теория и приложения.– 2023.– Т. **14**.– № 3.– С. 115–138. doi URL ↑<sub>15</sub>

Поступила в редакцию 30.10.2023;

одобрена после рецензирования 15.01.2024;

принята к публикации 16.01.2024;

опубликована онлайн 05.04.2024.

Рекомендовал к публикации

к.ф.-м.н. С. А. Романенко

### Информация об авторе:

Виктор Сергеевич Подлазов

Д. т. н., гл.н.с. Института проблем управления им. В.А. Трапезникова РАН, научные интересы: архитектуры интерконнекта и маршрутизация в суперкомпьютерных системах

0000-0002-9175-1138

e-mail: [podlazov@ipu.ru](mailto:podlazov@ipu.ru)

[podlazov@gmail.com](mailto:podlazov@gmail.com)

Декларация об отсутствии личной заинтересованности: *благополучие автора не зависит от результатов исследования.*

UDC 004.724.2 + 004.272.43

10.25209/2079-3316-2024-15-2-3-19

# Distributed ALUs based on photonic switches

Viktor Sergeevich **Podlazov**

V. A. Trapeznikov Institute of Control Sciences of RAS, Moscow, Russia

**Abstract.** The article examines a photonic network with distributed control, consisting of several nodes connected by a common channel, in which, during the transmission of one number, a single operation is performed on numbers that are transmitted in parallel by all nodes. Such operations as summing or finding the maximum (minimum) of numbers transmitted sequentially across binary bits are considered. It is assumed that the bits of numbers are transmitted by paraphase optical signals, and the common channel is built from photonic switches of these signals. (*In Russian*).

**Key words and phrases:** common channel, distributed control, photonic switch, photonic multiplexer and demultiplexer, calculation in a common channel, sequential numbers

2020 *Mathematics Subject Classification:* 65Y05; 68Q10

**For citation:** Viktor S. Podlazov. *Distributed ALUs based on photonic switches*. Program Systems: Theory and Applications, 2024, **15**:2(61), pp. 3–19. (*In Russ.*). [https://psta.psiras.ru/read/psta2024\\_2\\_3-19.pdf](https://psta.psiras.ru/read/psta2024_2_3-19.pdf)

## References

- [1] S. Stepanenko. “Structure and Implementation Principles of a Photonic Computer”, *EPJ Web of Conferences*, **224** (2019), id. 04002, 7 pp. [doi](#)

- [2] S. A. Stepanenko. *Optical logic element (options)*, Patent No 2 723 906 C1, 18.06.2020, id. 06 (In Russian). [URL](#)

- [3] S. M. Abramov, S. A. Stepanenko. “On approaches to developing software for a photonic computer”, Naciona’nyj Superkomp’yuternyj Forum (NSKF-2023) (Rossiya, Pereslavl’-Zaleskij, IPS imeni A.K. Ajlamazyana RAN, 28 novabrya–01 dekabrya 2023 goda) (In Russian). [URL](#)

- [4] I. V. Prangishvili, V. S. Podlazov, G. G. Stecyura. *Local microprocessor computer networks*, Glava 6, Nauka, M., 1984, 175 pp. (In Russian).

- [5] A. I. Stanley, G. Singh, J. Eke, H. Tsuda. “Mach–Zehnder interferometer: A review of a perfect all optical switching structure”, *Proceedings of the International Conference on Recent Cognizance in Wireless Communication & Image Processing*, eds. Afzalpulkar N., Srivastava V., Singh G., Bhatnagar D., Springer, New Delhi, 2016, ISBN 978-81-322-2638-3, pp. 415–425. [doi](#)

- [6] W. D. Sacher, W. M. J. Green, D. M. Gill, S. Assefa, T. Barwicz, M. Khater, Ed. Kiewra, C. Reinholtm, S. M. Shank, Yu. A. Vlasov, J. K. S. Poon. “Binary phase-shift keying by coupling modulation of microrings”, *Optics Express*, **22**:17 (2014), pp. 20252–20259. [doi](#)

- [7] W. M. J. Green, M. Yang, S. Assefa, Campenhout J. Van, B. G. Lee, C. V. Jahnes, F. E. Doany, C. L. Schow, J. A. Kash, Y. A. Vlasov. “Silicon electro-optic  $4 \times 4$  non-blocking switch array for on-chip photonic networks”, *Los Angeles, California United States, 6–10 March 2011*, OSA/OFC/NFOEC 2011, ISBN 978-1-55752-906-0, id. OThM1. [doi](#)

- [8] T.-H. Yen, Y.-J. Hung. “Fabrication-insensitive CWDM (de)multiplexer based on cascaded Mach-Zehnder interferometers on silicon-on-insulator”, *Journal of Lightwave Technology*, **39**:1 (2020), pp. 146–153. [doi](#)

- [9] Y. Gui, B. M. Nouri, M. Miscuglio, R. Amin, H. Wang, J. B. Khurgin, H. Dalir, Sorger V. J. . “100 GHz micrometer-compact broadband monolithic ITO Mach–Zehnder interferometer modulator enabling 3500 times higher packing density”, *Nanophotonics*, **11**:17 (2022), pp. 4001–4009. [doi](#)

- [10] K. Vytovtov, E. Barabanova, S. Zouhdi. “Optical switching cell based on metamaterials and ferrite films”, 12th International Congress on Artificial Materials for Novel Wave Phenomena (Metamaterials) (Espoo, Finland, August 2018–01 September 2018), 2018, pp. 424–426. [doi](#)

- [11] E. A. Barabanova, K. A. Vytovtov. “The control system elements of the new generation optical switching cell”, *Journal of Physics: Conference Series*, **1368**:2 (2019), id. 022002, 9 pp. [doi](#)

- [12] K. A. Vytovtov, E. A. Barabanova, V. S. Podlazov. “Model of next-generation optical switching system”, *Distributed Computer and Communication Networks*, DCCN 2018, Communications in Computer and Information Science, vol. **919**, Springer, Cham, ISBN 978-3-319-99447-5, pp. 377–386. [doi](#)

- [13] E. A. Barabanova, K. A. Vytovtov, V. M. Vishnevskiy, V. S. Podlazov. “High-capacity strictly non-blocking optical switches based on new dual principle”, 5th International Scientific Conference on Information, Control, and Communication Technologies (ICCT-2021) (Astrakhan, Russian Federation, 4–7 October 2021), *Journal of Physics: Conference Series*, **2091** (2021), id. 012040, 17 pp.

- [14] G. Roelkens, O. Raz, W. M. J. Green, S. Assefa, M. Tassaert, S. Keyvaninia, K. Vandoorne, Thourhout D. Van, R. Baets, Y. Vlasov. “Towards a low-power nanophotonic semiconductor amplifier heterogeneously integrated with SOI waveguides”, 7th IEEE International Conference on Group IV Photonics (Beijing, China, 01–03 September 2010), pp. 16–18.

- [15] V. S. Podlazov. “Multichannel non-blocking system area network with direct channels”, *Program Systems: Theory and Applications*, **13**:4(55) (2022), pp. 47–76 (In Russian).

- [16] V. S. Podlazov. “Multichannel non-blocking system area network with direct channels”, *Program Systems: Theory and Applications*, **14**:3 (2023), pp. 115–138 (In Russian).

## Жестовое управление полетом малого беспилотного летательного аппарата

Николай Сергеевич **Абрамов**<sup>1</sup>, Вита Викторовна **Саттарова**<sup>2</sup>,

Виталий Петрович **Фраленко**<sup>3</sup>, Михаил Вячеславович **Хачумов**<sup>4</sup>

<sup>1,3,4</sup> Институт программных систем им. А. К. Айламазяна РАН, Веськово, Россия

<sup>2</sup> Российский университет дружбы народов, Москва, Россия

<sup>4</sup> Российский государственный гуманитарный университет, Москва, Россия

<sup>4</sup> Федеральный исследовательский центр «Информатика и управление» РАН, Москва, Россия

<sup>4</sup> МИРЭА - Российский технологический университет, Москва, Россия

**Аннотация.** Рассмотрена задача построения жестовых команд для управления малым беспилотным летательным аппаратом, таким как квадрокоптер. Получаемые видеокамерой команды идентифицируются классификатором на основе сверточной нейронной сети, а мультимодальный интерфейс управления, оснащенный интеллектуальным реципиентом, преобразует их в команды управления квадрокоптером. Нейронные сети из библиотеки реальности нейронных сетей Ultralytics позволяют выделять целевые объекты в кадре в режиме реального времени. Команды управления квадрокоптером поступают в специализированную программу на смартфоне, разработанную на базе симулятора полетов DJI SDK, которая посыпает команды по радиоканалу дистанционного управления.

Исследовано качество распознавания разработанных жестовых команд для квадрокоптеров DJI Phantom 3 standard edition. Представлено краткое руководство в виде сценариев работы оператора с беспилотными транспортными средствами. Раскрыты перспективы жестового управления несколькими транспортными средствами в экстремальных условиях с учётом сложностей безопасности совместного полета и взаимодействия летательных аппаратов в ограниченном пространстве.

**Ключевые слова и фразы:** беспилотный летательный аппарат, управление, жесты, сверточная нейронная сеть, Ultralytics, интеллектуальный интерфейс, распознавание

**Благодарности:** Исследование выполнено за счет гранта Российского научного фонда № 21-71-10056, <https://rscf.ru/project/21-71-10056/>

**Для цитирования:** Абрамов Н. С., Саттарова В. В., Фраленко В. П., Хачумов М. В. Жестовое управление полетом малого беспилотного летательного аппарата // Программные системы: теория и приложения. 2024. Т. 15. № 2(61). С. 21–35. [https://psta.psiras.ru/read/psta2024\\_2\\_21-35.pdf](https://psta.psiras.ru/read/psta2024_2_21-35.pdf)

## Введение

В настоящее время большое количество исследований и разработок посвящено развитию беспилотных летательных аппаратов (БПЛА). Для повышения надежности и удобства взаимодействия с БПЛА в дополнение к типовым пультовым операциям управления применяют жестовые и речевые команды [1]. Для реализации такого подхода необходимы многомодальные человеко-машинные интерфейсы, адаптированные к различным типам БПЛА. Жесты подразделяются на статические и динамические и используются для передачи информации в компьютер с целью управления компьютером, летательным аппаратом, роботом и т.д.

В диссертационной работе [2] представлена комплексная методология захвата, отслеживания и распознавания динамических жестов в видео-потоке. В рамках этой методологии разработаны алгоритм захвата и отслеживания кисти человека в видеопотоке на сложном фоне; алгоритм и вычислительно-эффективная модель для распознавания жестов, основанная на нечетких конечных автоматах. Разработана методология мультимодального распознавания сцен, определяемых жестами, с использованием нечетких операторов агрегирования. Экспериментально показано, что предложенная архитектура системы распознавания динамических жестов позволяет с высокой степенью надежности распознавать в реальном времени жесты независимо от индивидуума.

В диссертационной работе [3] предложены метод извлечения изображения руки из дальностного изображения человека на основе анализа связности точек изображения в трехмерном пространстве; метод распознавания позиции кончиков пальцев и точек соединения пальцев с ладонью руки на основе анализа контура изображения руки; метод скелетизации дальностного изображения, основанный на непрерывном скелетном представлении бинарного изображения, поиске граничных точек фигуры и создании диаграммы Вороного для этих точек; метод распознавания статических и динамических жестов рук и пальцев руки для жестовой азбуки глухонемых.

В исследовании [4] представлено решение проблемы восстановления и отслеживания трехмерного положения, ориентации и полной артикуляции человеческой руки по данным от Kinect-сенсора. Решается задача оптимизации, в которой осуществляется поиск параметров модели руки, которые минимизируют расхождение между внешним видом и трехмерной структурой данных от сенсора. 3D-трекинг движения рук выполняется в реальном времени.

В работе [5] представлена техника взаимодействия, позволяющая с помощью жестов рук управлять функциями камеры, такими как панорамирование, наклон и затвор. В основе предложенной техники — алгоритм Лукаса-Канаде.

В исследовании [6] выполнена оценка возможности нейронных сетей помогать в распознавании жестов рук в арабском жестовом языке, проведены эксперименты с нейронными сетями прямого распространения и рекуррентными нейронными сетями. Предложенная система с полностью рекуррентной архитектурой демонстрирует точность 95% при распознавании статических жестов.

В работе [7] представлен интерфейс пользователя для распознавания жестов рук американского жестового языка с использованием буквосочетаний на пальцах. Жесты классифицируются с помощью метода случайных лесов (от англ. «random forest»). Классификатор жестов интегрирован с английским словарем для ускорения написания текстов.

В исследовании [8] представлен прототип мультимодальной системы, который интегрирует методы распознавания лица, жестов и речи для поддержки мультимодальной возможности взаимодействия человека с компьютером. Разработана многоуровневая система с несколькими камерами для наблюдения за лицом пользователя, жестами тела и пространственным расположением в комнате. Используя речевой ввод, система более точно воспринимает намерения пользователя.

В работе [9] описан механизм управления квадрокоптером с помощью жестов и поз. Этот механизм делает человеко-машинное взаимодействие более интуитивным, удобным и отзывчивым на потребности пользователя.

Управление жестовыми командами может осуществляться с использованием различных сенсорных устройств. Например, для квадрокоптера *Parrot AR.Drone 2.0*<sup>URL</sup> от компании Parrot в работе [10] была предложена бесконтактная система управления с использованием трехмерного сенсора Kinect. Однако, универсальным и распространенным видом современного устройства ввода информации является, несомненно, видеокамера. Перспективным шагом можно считать построение комбинированных интерфейсов, отличающихся большей надежностью. Например, такой интерфейс представлен в работе [11], где для распознавания жестов оператора БПЛА используется нейросетевая архитектура Yolo 5, а для обработки и распознавания речи — различные многослойные искусственные нейронные сети (ИНС).

Выделим несколько инструментальных средств распознавания образов.

Метод инвариантных моментов [12]. Здесь распознавание позиции и ориентации руки в бинарном изображении осуществляется посредством вычисления моментов изображения, при условии, что фон изображения однороден и рука является доминирующим объектом в изображении. Метод реализуется для 2D-и 3D-режимов и позволяет упростить процесс сравнения жеста с эталонами. Методы позволяют корректно, в пределах точности представления изображений, сравнивать два изображения. Инвариантный подход к распознаванию допускает точную математическую постановку задачи, позволяющую задавать классы объектов. Метод был практически применен в диссертационной работе [3].

Метод *DTW<sup>®</sup>* (англ. Dynamic Time Warping, алгоритм динамической трансформации временной шкалы). Идентификация формы осуществляется путем сравнения «скелета» руки с эталонами. Под скелетом здесь понимается набор опорных точек ладони, идентифицирующих положение ладони и пальцев. Для оценки степени схожести предварительно производится развертка скелетов, где по оси абсцисс откладываются номера точек в строгом соответствии с номерами их обхода в скелете, а по оси ординат координаты точек. После развертки расстояние между объектами оценивается за полиномиальное время с помощью алгоритма динамической трансформации шкалы времени.

Известно, что рекуррентная ИНС с архитектурой LSTM (Long Short-Term Memory) [13] показывает хорошие результаты при распознавании жестов, пример ее использования приведен в исследовании [14], где полученное значение показателя «точность» («accuracy») не менее 0.90, а в среднем 0.93. В работе [15] было проведено обучение нейронной сети Mask-RCNN для распознавания жестов рук, проанализированы существующие способы распознавания жестов, исследованы преимущества и недостатки рассмотренных методов. Предложена собственная архитектура сверточной нейронной сети для решения задачи классификации жестов. Проведена оценка точности работы сети в зависимости от расстояния между камерой и рукой, а также в зависимости от сложности жеста.

Предлагаемый в настоящей работе интерфейс управления БПЛА обеспечивает повышенную надежность и гибкость за счет использования стандартного кнопочного управления в комбинации с голосовыми и жестовыми командами. При управлении со стационарного рабочего места управление оказывается максимально эффективным. Однако, беспилотники могут работать и в режиме передачи управления людям, находящимся в местах, где имеются пожары, задымления, высокий уровень шума. Именно в этих условиях важно получать надежно команды управления, по этой причине и вводится мультимодальность управления,

позволяющая продублировать команды, при этом с помощью ИНС определяется степень уверенности и выбирается наиболее вероятная команда.

Управление БПЛА с помощью жестов включает несколько ключевых элементов:

- (1) видеокамера, способная регистрировать жесты пользователя;

- (2) алгоритмы распознавания, способные классифицировать и преобразовать жест в команду;

- (3) команды управления, осуществляющие преобразование набора жестов в команды БПЛА;

- (4) интеллектуальный интерфейс – программно-техническое средство, через которое пользователь взаимодействует с аппаратом.

### **Оценка эффективности управления квадрокоптером на основе системы жестовых команд**

В настоящем исследовании исходным материалом служили базовые команды управления. Рассматривались движения по всем направлениям пространства, включая перемещение, поворот вокруг вертикальной оси, взлет и посадку. Для экспериментов с управлением жестами использовался квадрокоптер модели *DJI Phantom 3 Standard Edition*<sup>®URL</sup>. Данный аппарат оснащен многофункциональной двухповоротной видеокамерой. Общий вид квадрокоптера и его основные характеристики представлены в таблице 1.

Таблица 1. Общий вид и основные характеристики задействованного БПЛА

| Квадрокоптер DJI Phantom 3 Standard Edition                                         | Основные характеристики                                                                                                                                                                                                                  |

|-------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|  | <p>(а) стабилизированный 3-осевой подвес с камерой;</p> <p>(б) встроенная камера: 2.7K видео и 12MP фото;</p> <p>(в) радиоканал WiFi 2.4G;</p> <p>(г) дальность связи 1 км;</p> <p>(д) интеллектуальный аккумулятор 15.2 V, 480 mAh.</p> |

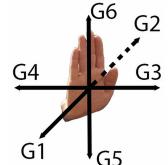

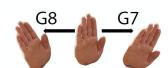

Предлагаемая система команд управления БПЛА приведена в таблице 2.

ТАБЛИЦА 2. Система команд для управления БПЛА

| Команда     | Назначение                                                                       | Описание способа управления                                                                                                      | Вид жеста                                                                           |

|-------------|----------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|

| Взлет       | Взлет на высоту 2.3 метра.                                                       | Жестовая команда « <i>палец вверх</i> ».                                                                                         |    |

| Приземление | Снижение и посадка в текущих координатах.                                        | Жестовая команда « <i>палец вниз</i> ».                                                                                          |    |

| Перемещение | Перемещение по трем осям пространства.                                           | Перемещение ладони по трем осям в шести направлениях: G1 – вперед, G2 – назад, G3 – влево, G4 – вправо, G5 – вниз, G6 – вверх.   |    |

| Домой       | Взлет на высоту 30 м. и возврат по прямой в координаты начальной точки, посадка. | Жестовая команда « <i>руки, сложенные в форме крыши</i> », команда может выполняться автоматически в случае потери связи с БПЛА. |    |

| Поворот     | Поворот вокруг оси рыскания.                                                     | Наклон ладони по двум направлениям: G7 – поворот вокруг оси против часовой стрелки, G8 – поворот вокруг оси по часовой стрелке.  |  |

| Остановка   | Прекращение движения (зависание в воздухе).                                      | Жестовая команда « <i>поднятый кулак</i> ».                                                                                      |  |

Инструкции для БПЛА, сформированные наземной станцией после обработки жестовых команд оператора, поступают в специализированную программу на смартфоне, разработанную на базе DJI SDK, которая посыпает команды через пульт и далее радиоканал.

Для оценки возможностей актуальной версии 8.1.47 программного пакета *Ultralytics*<sup>URL</sup> по локализации целевых объектов (жестов для управления БПЛА) проведен ряд экспериментов с поддерживающими этим пакетом конфигурациями ИНС: Yolo 5, Yolo 8, Yolo 8 Ghost, Yolo 8 Rtdetr, Yolo 9 и оригинальной архитектурой Rtdetr от Baidu [16]. Во всех случаях, кроме последнего и предпоследнего, использовались *m*-модификации ИНС, для Yolo 9 – *c*-модификация, а в последнем случае – *l*-модификация. Работа ИНС проверялась на собственном датасете с командами для управления БПЛА, содержащем жестовые команды «взлет», «приземление», «остановка» и «домой», применяемые при мультимодальном управлении БПЛА [11]; использовалась разметка с помощью *ориентированных*<sup>URL</sup> и *неориентированных*<sup>URL</sup> прямоугольных областей; всего 247 обучающих изображений и 122 тестовых. Тестирование выполнялось в режиме с половинной точностью (параметр *half*=True).

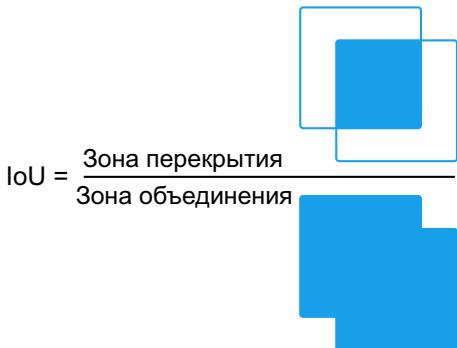

Повышение параметра *imgsz* (влияет на масштабирование поступающих изображений) с исходных 640 пикселей, заложенных по умолчанию в программный код библиотеки, до 1120 позволяет уверенно распознавать жесты, показываемые оператором на удалении. В процессе валидации результатов с пороговым значением *conf* (уровень уверенности ИНС) отсеиваются те зоны, потенциально содержащие жест, для которых  $conf \geq 0.01$ . Среди оставшихся выбираются те, у которых значение  $iou \geq 0.7$  (уровень пересечения с оригинальным жестом в зоне). Значения параметров подобраны экспериментально.

Для исследования качества распознавания на вход ИНС подавались изображения, измененные до размера 1120x640 пикселей. При тестировании использовалось следующее аппаратное обеспечение: процессор общего назначения Intel Core i7-6850k (6 ядер / 12 потоков, 4 ГГц), оперативная память 32 ГБ, видеокарта Nvidia GeForce RTX 3060.

Результаты решения задачи выделения управляющих жестов (для неориентированных прямоугольников) представлены в таблице 3. Основные показатели качества – mAP50-95 и значение F1-меры, достигаемой при указанном в таблице пороге уверенности.

ТАБЛИЦА 3. Результаты работы ИНС для локализации управляющих жестов (для неориентированных прямоугольников)

| Вид ИНС        | Команда     | Точность     | Полнота      | mAP50-95 | F1   | Порог уверенности |

|----------------|-------------|--------------|--------------|----------|------|-------------------|

| Yolo 5         | взлет       | <b>1.000</b> | 0.965        | 0.871    |      |                   |

|                | приземление | 0.999        | <b>1.000</b> | 0.869    |      |                   |

|                | остановка   | 0.997        | <b>1.000</b> | 0.841    |      |                   |

|                | домой       | 0.997        | <b>1.000</b> | 0.802    |      |                   |

|                | все         | 0.998        | 0.991        | 0.846    | 0.99 | 0.723             |

| Yolo 8         | взлет       | <b>1.000</b> | 0.924        | 0.749    |      |                   |

|                | приземление | <b>1.000</b> | 0.850        | 0.659    |      |                   |

|                | остановка   | <b>1.000</b> | 0.997        | 0.694    |      |                   |

|                | домой       | 0.928        | <b>1.000</b> | 0.591    |      |                   |

|                | все         | 0.982        | 0.943        | 0.673    | 0.96 | 0.583             |

| Yolo 9         | взлет       | <b>1.000</b> | 0.999        | 0.868    |      |                   |

|                | приземление | 0.971        | <b>1.000</b> | 0.853    |      |                   |

|                | остановка   | <b>1.000</b> | <b>1.000</b> | 0.851    |      |                   |

|                | домой       | <b>1.000</b> | <b>1.000</b> | 0.854    |      |                   |

|                | все         | 0.993        | <b>1.000</b> | 0.856    | 1.00 | 0.242             |

| Yolo 8 Ghost   | взлет       | <b>1.000</b> | <b>1.000</b> | 0.812    |      |                   |

|                | приземление | 0.996        | <b>1.000</b> | 0.861    |      |                   |

|                | остановка   | <b>1.000</b> | <b>1.000</b> | 0.829    |      |                   |

|                | домой       | 0.997        | <b>1.000</b> | 0.825    |      |                   |

|                | все         | 0.998        | <b>1.000</b> | 0.831    | 1.00 | 0.795             |

| Yolo 8 Rtdetr  | взлет       | 0.998        | <b>1.000</b> | 0.857    |      |                   |

|                | приземление | 0.986        | <b>1.000</b> | 0.794    |      |                   |

|                | остановка   | 0.998        | <b>1.000</b> | 0.758    |      |                   |

|                | домой       | 0.997        | <b>1.000</b> | 0.864    |      |                   |

|                | все         | 0.995        | <b>1.000</b> | 0.818    | 1.00 | 0.861             |

| Rtdetr (Baidu) | взлет       | 0.971        | <b>1.000</b> | 0.805    |      |                   |

|                | приземление | 0.882        | <b>1.000</b> | 0.736    |      |                   |

|                | остановка   | 0.995        | <b>1.000</b> | 0.634    |      |                   |

|                | домой       | 0.954        | <b>1.000</b> | 0.756    |      |                   |

|                | все         | 0.950        | <b>1.000</b> | 0.733    | 0.97 | 0.616             |

В случае использования неориентированных прямоугольников архитектуры Yolo 8 Ghost, Yolo 8 Rtdetr и Yolo 9 обеспечили безошибочное выделение всех жестовых команд без ложных срабатываний, однако, максимальную точность локализации обеспечивает новая Yolo 9, она же

имеет самое высокое значение mAP50-95 = 0.856. Детальное исследование данных, получаемых от ИНС, показало, что иногда в кадре находится несколько объектов (не более двух, как показали эксперименты), однако за счет порога уверенности можно добиться полного исключения ложного обнаружения. В данном случае Yolo 9 обрабатывает кадр видеопотока за 19.5 мс.

Результаты решения задачи выделения управляющих жестов (для ориентированных прямоугольников) представлены в таблице 4. Вариант Yolo 8 Rtdetr исключен из рассмотрения ввиду того, что слой RTDETR-Decoder в этой архитектуре нельзя заменить на OBB-слой.

ТАБЛИЦА 4. Результаты работы ИНС для локализации управляющих жестов (для ориентированных прямоугольников)

| Вид ИНС        | Команда     | Точность     | Полнота      | mAP50-95 | F1          | Порог уверенности |

|----------------|-------------|--------------|--------------|----------|-------------|-------------------|

| Yolo 5         | взлет       | <b>1.000</b> | <b>1.000</b> | 0.914    |             |                   |

|                | приземление | <b>1.000</b> | <b>1.000</b> | 0.978    |             |                   |

|                | остановка   | 0.996        | <b>1.000</b> | 0.965    |             |                   |

|                | домой       | 0.996        | <b>1.000</b> | 0.935    |             |                   |

|                | все         | 0.988        | <b>1.000</b> | 0.948    | <b>1.00</b> | 0.785             |

| Yolo 8         | взлет       | 0.994        | <b>1.000</b> | 0.937    |             |                   |

|                | приземление | <b>1.000</b> | <b>1.000</b> | 0.977    |             |                   |

|                | остановка   | 0.998        | <b>1.000</b> | 0.951    |             |                   |

|                | домой       | <b>1.000</b> | <b>1.000</b> | 0.961    |             |                   |

|                | все         | 0.998        | <b>1.000</b> | 0.956    | <b>1.00</b> | 0.793             |

| Yolo 9         | взлет       | <b>1.000</b> | <b>1.000</b> | 0.918    |             |                   |

|                | приземление | <b>1.000</b> | <b>1.000</b> | 0.977    |             |                   |

|                | остановка   | <b>1.000</b> | <b>1.000</b> | 0.960    |             |                   |

|                | домой       | 0.993        | <b>1.000</b> | 0.913    |             |                   |

|                | все         | 0.998        | <b>1.000</b> | 0.942    | <b>1.00</b> | 0.747             |

| Yolo 8 Ghost   | взлет       | 0.988        | <b>1.000</b> | 0.924    |             |                   |

|                | приземление | <b>1.000</b> | <b>1.000</b> | 0.961    |             |                   |

|                | остановка   | 0.998        | <b>1.000</b> | 0.936    |             |                   |

|                | домой       | 0.996        | <b>1.000</b> | 0.926    |             |                   |

|                | все         | 0.996        | <b>1.000</b> | 0.937    | <b>1.00</b> | 0.796             |

| Rtdetr (Baidu) | взлет       | 0.991        | <b>1.000</b> | 0.928    |             |                   |

|                | приземление | 0.999        | <b>1.000</b> | 0.971    |             |                   |

|                | остановка   | 0.998        | <b>1.000</b> | 0.964    |             |                   |

|                | домой       | <b>1.000</b> | <b>1.000</b> | 0.949    |             |                   |

|                | все         | 0.997        | <b>1.000</b> | 0.953    | <b>1.00</b> | 0.745             |

Все варианты архитектур обеспечили 100%-ые полноту и F1-меру.

Однако, Yolo 8 обеспечила самое высокое значение показателя mAP50-95 = 0.956 (среднее для всех жестов) в сочетании с точностью 0.998. Если сравнивать эту ИНС с лучшей для неориентированных прямоугольников, переход к ориентированным обеспечил рост mAP50-95 на величину 0.1, что весьма существенно. Yolo 8 обрабатывает кадр видеопотока за 12.8 мс. Yolo 8 Ghost решает ту же задачу за 9.6 мс, то есть позволяет снизить временные затраты на 25%. Учитывая, что в данной задаче обе сети обеспечивают F1-меру 100%, приоритет следует отдать Yolo 8 Ghost.

Далее приведем краткий сценарий работы оператора с БПЛА:

- (1) подготовить полетный план: задать координаты доступных для полета точек (широта, долгота, высота);

- (2) активировать составляющие систему: БПЛА, пульт (для связи БПЛА с наземной станцией), мобильное приложение (клиент) и главную программу (сервер); для управления жестами к серверу должна быть подключена видеокамера;

- (3) в мобильном приложении выбрать настройки: установить порт для связи с сервером и координаты «домашней точки», флаги передачи телеметрической информации, видеопотока с бортовой камеры БПЛА и использования режима симулятора компании-разработчика квадрокоптера; после этого установится связь между сервером и БПЛА, и главная программа будет готова принимать команды оператора;

- (4) зафиксировать положение оператора в кадре видеокамеры сервера таким образом, чтобы в кадр попадали руки оператора;

- (5) для управления жестами оператор показывает в видеокамеру один из них: «взлет», «приземление», «домой», «остановка»; при этом следует показывать жест несколько секунд: это сделано для того, чтобы исключить ложные срабатывания системы распознавания;

- (6) посредством нажатия левой кнопки мыши по кнопкам интерфейса главной программы оператор может отдать команды БПЛА в соответствии с таблицей 2;

- (7) посредством зажатия левой кнопки мыши на трехмерной карте местности полета в центральной части интерфейса, в которой отображено текущее положение БПЛА, осуществляется смещение «камеры-наблюдателя» 3D-сцены; зажатие колеса мыши позволяет поворачивать сцену, а зажатие правой кнопки мыши – позволяет управлять «зумом»;

- (8) после выполнения полетного задания оператору следует дать команду «приземление» или «домой» любым описанным выше способом;

- (9) после завершения полета выключить БПЛА, пульт, мобильное приложение и остановить работу сервера.

## Заключение

Рассмотрен и прошел первичную апробацию подход к управлению малым БПЛА типа квадрокоптер на основе жестовых команд. Базовые команды управления движением летательного аппарата включают перемещения в пространстве, повороты вокруг вертикальной оси, взлет и посадку. Эксперименты показали достаточную для практического использования точность распознавания ряда жестовых команд с применением сверточных искусственных нейронных сетей, соответствующую зарубежным аналогам [4–9, 15], задача полностью решена с помощью архитектур Yolo 8 Ghost и Yolo 9 для режимов с ориентированными и неориентированными прямоугольниками для выделения зон с жестами.

Дальнейшим расширением подхода может служить управление жестами несколькими БПЛА. Выполнение сложных групповых заданий вызывает необходимость решения задач, связанных с безопасным совместным полетом и взаимодействием автономных летающих роботов в процессе функционирования на одних и тех же участках. Например, когда в условиях пожара перед несколькими БПЛА в процессе выполнения спасательных работ возникает необходимость в совместном поднятии в воздух тяжелого объекта для смены его местоположения. В этом случае каждый БПЛА должен быть способным к коллективному взаимодействию элементов группы как интеллектуальных агентов. Подобные сложные задачи интеллектуального взаимодействия автономных БПЛА требуют расширения системы команд для придания специфики каждому летательному аппарату. Кроме того, требуется наделение интерфейса и БПЛА некоторыми интеллектуальными функциями.

## Список использованных источников

- [1] Абрамов Н. С., Талалаев А. А., Фраленко В. П., Хачумов М. В. *Система мультимодального управления и визуализации полета беспилотного летательного аппарата* // Авиакосмическое приборостроение.– 2023.– № 9.– С. 3–11. doi: [↑22](#)

- [2] Алфимцев А. Н. *Разработка и исследование методов захвата, отслеживания и распознавания динамических жестов*, Диссертация на соискание ученой степени кандидата технических наук.– М.– 2008.– 167 с. [↑22](#)

- [3] Нагапетян В. Э. *Методы распознавания жестов руки на основе анализа дальностных изображений*, Диссертация на соискание ученой степени кандидата физико-математических наук.– М.– 2008.– 117 с. [↑22, 24](#)

- [4] Oikonomidis I., Kyriazis N., Argyros A. A. *Efficient model-based 3D tracking of hand articulations using Kinect* // Proceedings of the 22nd British Machine Vision Conference 2011, BMVC'11 (Dundee, UK, August 29–September 2, 2011).– 2011.– ISBN 1-901725-43-X.– 11 pp. [URL](#) doi: [↑22, 31](#)

- [5] Shaowei C., Tanaka J. *Interacting with a self-portrait camera using motion-based hand gestures* // Proceedings of the 11th Asia-Pacific Conference on Computer-Human Interaction 2013, APCHI'13 (Bangalore, India, September 24–27, 2013), New York: ACM.– 2013.– ISBN 978-1-4503-2253-9.– Pp. 93–101. doi ↑<sub>23, 31</sub>

- [6] Maraqa M. R., Al-Zboun F., Dhyabat M., Zitar R. A. *Recognition of Arabic Sign Language (ArSL) using recurrent neural networks* // Journal of Intelligent Learning Systems and Applications.– 2012.– Vol. 4.– No. 1.– Pp. 41–52. doi ↑<sub>23, 31</sub>

- [7] Pugeault N., Bowden R. *Spelling it out: real-time ASL fingerspelling recognition* // Proceedings of the IEEE International Conference on Computer Vision Workshops 2011, ICCV'11 (Barcelona, Spain, 06–13 November 2011).– 2011.– Pp. 1114–1119. doi ↑<sub>23, 31</sub>

- [8] Zhao R., Wang K., Divekar R., Rouhani R., Su H., Ji Q. *An immersive system with multi-modal human-computer interaction* // Proceedings of the 13th IEEE International Conference on Automatic Face & Gesture Recognition 2018 (Xi'an, China, 15–19 May 2018).– 2018.– Pp. 517–524. doi ↑<sub>23, 31</sub>

- [9] Sanna A., Lamberti F., Paravati G., Manuri F. *A kinect-based natural interface for quadrotor control* // Entertainment Computing.– 2013.– Vol. 4.– No. 3.– Pp. 179–186. doi ↑<sub>23, 31</sub>

- [10] Нагапетян В. Э., Хачумов В. М. *Распознавание жестов руки в задаче бесконтактного управления беспилотным летательным аппаратом* // Автометрия.– 2015.– Т. 51.– № 2.– С. 103–109. ✩ ↑<sub>23</sub>

- [11] Абрамов Н. С., Емельянова Ю. Г., Таалаев А. А., Фраленко В. П., Хачумов М. В. *Архитектура мультимодального интерфейса для управления беспилотным летательным аппаратом* // Известия высших учебных заведений. Авиационная техника.– 2022.– № 3.– С. 55–63. ✩ ↑<sub>23, 27</sub>

- [12] Hu M. K. *Visual pattern recognition by moment invariants* // IRE Transactions on Information Theory.– 1962.– Vol. 8.– No. 2.– Pp. 179–187. doi ↑<sub>24</sub>

- [13] Hochreiter S., Schmidhuber J. *Long short-term memory* // Neural Computation.– 1997.– Vol. 9.– No. 8.– Pp. 1735–1780. doi ↑<sub>24</sub>

- [14] Жуковская В. А., Пятаева А. В. *Рекуррентная нейронная сеть для распознавания жестов русского языка с учетом языкового диалекта Сибирского региона* // Графикон 2022: материалы 32-й Международной конференции по компьютерной графике и машинному зрению (Рязань, 19–22 сентября 2022 г.).– 2022.– С. 538–547. URL doi ↑<sub>24</sub>

- [15] Булыгин Д. А., Мамонова Т. Е. *Распознавание жестов рук в режиме реального времени* // Научный вестник НГТУ.– 2020.– № 1(78).– С. 25–40. doi ↑<sub>24, 31</sub>

- [16] Zhao Y., Lv W., Xu S., Wei J., Wang G., Dang Q., Liu Y., Chen J., *DETRs beat YOLOs on real-time object detection.*– 2023.– 14 pp. arXiv ✩ 2304.08069 [cs.CV] doi ↑<sub>27</sub>

Поступила в редакцию 09.02.2024;

одобрена после рецензирования 13.03.2024;

принята к публикации 17.03.2024;

опубликована онлайн 22.04.2024.

Рекомендовал к публикации

д. ф.-м. н. А. М. Елизаров

## Информация об авторах:

Николай Сергеевич Абрамов

к.т.н., ведущий научный сотрудник ИЦМС ИПС им. А.К. Айламазяна РАН. Область научных интересов: математические методы синтеза, обработки и анализа изображений и сигналов, искусственный интеллект и принятие решений, интеллектуальный анализ данных и распознавание образов, геометрия.

0000-0002-1612-3879

e-mail: [n-say@nsa.pereslavl.ru](mailto:n-say@nsa.pereslavl.ru)

Вита Викторовна Саттарова

Студент Российской университета дружбы народов им. Патриса Лумумбы. Область научных интересов: интеллектуальный анализ данных и распознавание образов, искусственный интеллект и принятие решений, управление робототехническими системами.

0009-0008-0425-6958

e-mail: [1032201655@pfur.ru](mailto:1032201655@pfur.ru)

Виталий Петрович Фраленко

Кандидат технических наук, ведущий научный сотрудник ИЦМС ИПС им. А.К. Айламазяна РАН. Область научных интересов: интеллектуальный анализ данных и распознавание образов, искусственный интеллект и принятие решений, параллельно-конвейерные вычисления, сетевая безопасность, диагностика сложных технических систем, графические интерфейсы.

0000-0003-0123-3773

e-mail: [alarmod@pereslavl.ru](mailto:alarmod@pereslavl.ru)

Михаил Вячеславович Хачумов

Кандидат физико-математических наук, старший научный сотрудник ИЦМС ИПС им. А.К. Айламазяна РАН, старший научный сотрудник ФИЦ «Информатика и управление» РАН, доцент РУДН им. Патриса Лумумбы, доцент МИРЭА. Область научных интересов: интеллектуальный анализ данных и распознавание образов, искусственный интеллект и принятие решений, управление робототехническими системами.

0000-0001-5117-384X

e-mail: [khmike@inbox.ru](mailto:khmike@inbox.ru)

*Авторы внесли равный вклад в подготовку публикации.*

*Декларация об отсутствии личной заинтересованности: благополучие авторов не зависит от результатов исследования.*

UDC 004.93:004.35

10.25209/2079-3316-2024-15-2-21-35

## Gesture control of small unmanned aerial vehicle flight

Nikolai Sergeevich **Abramov**<sup>1</sup>, Vita Viktorovna **Sattarova**<sup>2</sup>,

Vitaly Petrovich **Fralenko**<sup>3</sup>, Mikhail Vyacheslavovich **Khachumov**<sup>4</sup>

<sup>1,3,4</sup> Ailamazyan Program Systems Institute of RAS, Ves'kovo, Russia

<sup>2</sup> RUDN University, Moscow, Russia

<sup>4</sup> Russian state university for the humanities, Moscow, Russia

<sup>4</sup> Federal Research Center "Computer Science and Control" of RAS, Moscow, Russia

<sup>4</sup> MIREA - Russian Technological University, Moscow, Russia

**Abstract.** The problem of constructing gesture commands for controlling a small unmanned aerial vehicle, such as a quadcopter, is considered. Commands coming from a video camera are identified by a classifier based on a convolutional neural network, and the multimodal control interface equipped with an intelligent solver converts them into control commands for the quadcopter. Neural networks from the Ultralytics neural network library allow selecting targets in a frame in real-time. The commands are sent to a specialized program on a smartphone, developed on the basis of DJI SDK flight simulators, which then sends commands via the remote control channel.

The quality of recognition of developed gesture commands for DJI Phantom 3 standard edition quadcopters is investigated, and a brief guide in the form of operator work scenarios with unmanned vehicles is provided. The prospects of gesture control of several vehicles in extreme conditions have been revealed, considering the complex safety challenges of joint flight and interaction of aircraft in confined space. (*In Russian*).

**Key words and phrases:** unmanned aerial vehicle, control, gestures, convolutional neural network, Ultralytics, intelligent interface, recognition

2020 *Mathematics Subject Classification:* 68T45; 68T07, 68T40

**Acknowledgments:** This work was financially supported by the Russian Science Foundation, project № 21–71–10056, <https://rscf.ru/project/21-71-10056/>

**For citation:** Nikolai S. Abramov, Vita V. Sattarova, Vitaly P. Fralenko, Mikhail V. Khachumov. *Gesture control of small unmanned aerial vehicle flight*. Program Systems: Theory and Applications, 2024, **15**:2(61), pp. 21–35. (*In Russ.*). [https://psta.psiras.ru/read/psta2024\\_2\\_21-35.pdf](https://psta.psiras.ru/read/psta2024_2_21-35.pdf)

## References

- [1] N. S. Abramov, A. A. Talalaev, V. P. Fralenko, M. V. Xachumov. “Multimodal control and visualization system for unmanned aerial flight”, *Aviakosmicheskoe priborostroenie*, 2023, no. 9, pp. 3–11 (in Russian). [doi](#)

- [2] A. N. Alfimcev. *Development and research of methods for capturing, tracking and recognizing dynamic gestures*, Dissertaciya na soiskanie uchenoj stepeni kandidata texnicheskix nauk, M., 2008, 167 pp. (in Russian).

- [3] V. E. Nagapetyan. *Hand gesture recognition methods based on range image analysis*, Dissertaciya na soiskanie uchenoj stepeni kandidata fiziko-matematicheskix nauk, M., 2008, 117 pp. (in Russian).

- [4] I. Oikonomidis, N. Kyriazis, A. A. Argyros. “Efficient model-based 3D tracking of hand articulations using Kinect”, *Proceedings of the 22nd British Machine Vision Conference 2011*, BMVC’11 (Dundee, UK, August 29–September 2, 2011), 2011, ISBN 1-901725-43-X, 11 pp. [URL](#) [doi](#)

- [5] C. Shaowei, J. Tanaka. “Interacting with a self-portrait camera using motion-based hand gestures”, *Proceedings of the 11th Asia-Pacific Conference on Computer-Human Interaction 2013*, APCHI’13 (Bangalore, India, September 24–27, 2013), ACM, New York, 2013, ISBN 978-1-4503-2253-9, pp. 93–101. [doi](#)

- [6] M. R. Maraqa, F. Al-Zboun, M. Dhyabat, R. A. Zitar. “Recognition of Arabic Sign Language (ArSL) using recurrent neural networks”, *Journal of Intelligent Learning Systems and Applications*, 4:1 (2012), pp. 41–52. [doi](#)

- [7] N. Pugeault, R. Bowden. “Spelling it out: real-time ASL fingerspelling recognition”, *Proceedings of the IEEE International Conference on Computer Vision Workshops 2011*, ICCV’11 (Barcelona, Spain, 06–13 November 2011), 2011, pp. 1114–1119. [doi](#)

- [8] R. Zhao, K. Wang, R. Divekar, R. Rouhani, H. Su, Q. Ji. “An immersive system with multi-modal human-computer interaction”, *Proceedings of the 13th IEEE International Conference on Automatic Face & Gesture Recognition 2018* (Xi’an, China, 15–19 May 2018), 2018, pp. 517–524. [doi](#)

- [9] A. Sanna, F. Lamberti, G. Paravati, F. Manuri. “A kinect-based natural interface for quadrotor control”, *Entertainment Computing*, 4:3 (2013), pp. 179–186. [doi](#)

- [10] V. E. Nagapetyan, V. M. Khachumov. “Gesture recognition in the problem of contactless control of an unmanned aerial vehicle”, *Optoelectronics, Instrumentation and Data Processing*, 51:2 (2015), pp. 192–197. [doi](#)

- [11] N. S. Abramov, Yu. G. Emel’yanova, A. A. Talalaev, V. P. Fralenko, M. V. Khachumov. “Multimodal interface architecture for unmanned aerial vehicle control”, *Russian Aeronautics*, 65:3 (2022), pp. 498–506. [doi](#)

- [12] M. K. Hu. “Visual pattern recognition by moment invariants”, *IRE Transactions on Information Theory*, 8:2 (1962), pp. 179–187. [doi](#)

- [13] S. Hochreiter, J. Schmidhuber. “Long short-term memory”, *Neural Computation*, 9:8 (1997), pp. 1735–1780. [doi](#)

- [14] V. A. Zhukovskaya, A. V. Pyataeva. “Recurrent neural network for recognition of gestures of the Russian language, taking into account the language dialect of the Siberian region”, *GrafiKon 2022: materialy 32-j Mezhdunarodnoj*

*konferencii po komp'yuternoj grafike i mashinnomu zreniyu* (Ryazan', 19–22 sentyabrya 2022 g.), 2022, pp. 538–547 (in Russian).

- [15] D. A. Bulygin, T. E. Mamonova. “Recognition of hand gestures in real time”, *Nauchnyj vestnik NGTU*, 2020, no. 1(78), pp. 25–40 (in Russian).

- [16] Y. Zhao, W. Lv, S. Xu, J. Wei, G. Wang, Q. Dang, Y. Liu, J. Chen., *DETRs beat YOLOs on real-time object detection*, 2023, 14 pp. arXiv 2304.08069 [cs.CV]

## Систематический обзор методов составления тестовых инвариантов

Софья Федоровна Якушева<sup>1✉</sup>, Антон Сергеевич Хританков<sup>2</sup>

<sup>1,2</sup> Московский физико-технический институт, Москва, Россия

<sup>2</sup> Высшая школа экономики, Москва, Россия

**Аннотация.** Тестирование инвариантами (metamorphic testing) – один из наиболее эффективных методов тестирования программ, для которых сложно подбирать тестовые примеры и формулировать тестовые оракулы. При тестировании инвариантами вместо проверки правильности вывода программы на отдельных наборах входных данных проверяется выполнение тестового инварианта (metamorphic relation) – функции от нескольких наборов исходных данных и соответствующих им ответов программы. Составление тестовых инвариантов требует понимания решаемой программой задачи и творческого подхода.

Предлагаемый систематический обзор посвящён выявлению широкоприменимых методик получения инвариантов и повторяющихся приёмов составления инвариантов в разных научных областях. На основе проведенного анализа предложена классификация инвариантов на шесть основных типов, выявлены типовые преобразования исходных данных, используемые при составлении инвариантов в нескольких областях знаний. Результаты обзора будут полезны исследователям в применении тестирования инвариантами на практике к верификации научных программ и алгоритмов машинного обучения.

*(Связанные тексты статьи на русском и на английском языках)*

**Ключевые слова и фразы:** тестирование инвариантами, тестовый инвариант, тестирование программного обеспечения, проблема формулирования тестового оракула

**Для цитирования:** Якушева С.Ф., Хританков А.С. *Систематический обзор методов составления тестовых инвариантов* // Программные системы: теория и приложения. 2024. Т. 15. №2(61). С. 37–86. (Русс.+англ.). [https://psta.psiras.ru/read/psta2024\\_2\\_37-86.pdf](https://psta.psiras.ru/read/psta2024_2_37-86.pdf)

## Введение

Контроль качества программного обеспечения (ПО) является важной частью процесса разработки. На этапе контроля проверяется, что ПО соответствует всем предъявленным к ней требованиям, а значит, будет вести себя ожидаемым и заранее известным образом. Отклонения поведения программного обеспечения от заявленных требований регулярно становятся причинами авиационных происшествий, аварий с участием самоуправляемых автомобилей, неудач космических миссий, нарушений безопасности данных [1]. Несоответствие требованиям является веским основанием для доработки разрабатываемой системы или выведения из эксплуатации уже используемой.

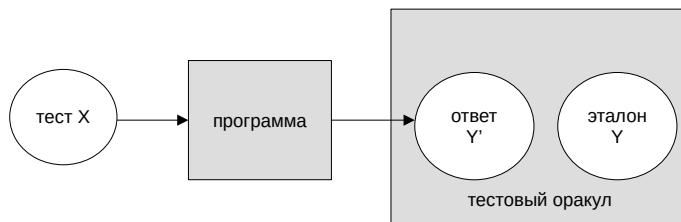

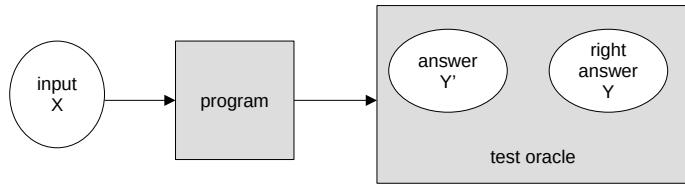

Тестирование – один из методов контроля качества программ в процессе разработки. Тестирование позволяет выявлять некорректное или ошибочное поведение программы, нарушения функциональных и нефункциональных требований, не предусмотренные документацией сценарии использования. Тестовым оракулом (test oracle) [2] называется функция, которая определяет правильность ответа программы. Простейший тестовый оракул сравнивает ответ программы с заранее известным эталоном (см. рисунок 1). Более сложным примером является проверка правильности найденного гамильтонова пути в графе: достаточно проверить наличие в пути всех вершин графа и наличие рёбер между соседними парами вершин пути, эталон для такой проверки не требуется. В плохо формализуемых случаях, если требования сформулированы неточно или требуется высокий уровень экспертизы, то в качестве тестового оракула могут выступать пользователь, эксперт, другая программа.

Рисунок 1. Пример проверки правильности прохождения теста. В роли оракула выступает сравнение ответа с эталоном.

При тестировании научных, недетерминированных, распределенных программных комплексов существенным затруднением является так называемая проблема формулирования тестового оракула. Проблема

формулирования тестового оракула (test oracle problem) [3] состоит в сложности составления тестовых оракулов – в частности, автоматических. Она актуальна для задач, требующих полного перебора для нахождения точного решения, например, в биоинформатике и комбинаторике; задач машинного обучения из-за затратности процесса сбора и разметки тестовых выборок; задач создания художественных объектов из-за необходимости привлечения человека для оценки выполнения плохо сформулированных требований. Тем не менее, были предложены различные методы так или иначе решить эту проблему, например, тестирование свойств (property-based testing), в котором проверяется выполнение заданного соотношения между входами и выходами программы и, как его разновидность, тестирование инвариантами (metamorphic testing).

## 1. Тестирование инвариантами

### 1.1. Определение и примеры